串扰是通过近电场(电容耦合)和磁场(电感耦合)在相邻导体之间耦合的噪声。尽管任何相邻导体都表现出串扰,但是当它出现在强干扰信号和敏感信号之间时,对信号完整性将造成很大的影响。

串扰的再定义:

攻击者=高振幅+高频+短上升时间

受害者=低振幅+高阻抗

某些信号由于其性质或在电路中的功能而对串扰特别敏感,这些信号是潜在的串扰受害者 ,如:

a、模拟信号:与数字信号相比,它们对噪声更敏感,尤其是在振幅较低的情况下。

b、高阻抗控制信号:使能,复位,振荡器和反馈信号是控制类信号。如果此类信号是 由低阻抗源产生的,则它们很容易受到电容串扰的干扰。

另一类信号很容易在受害者身上引起噪声,并被认为是串扰的潜在攻击者 。为了识别潜在的攻击者,请记住串扰是由PCB走线之间的耦合电容和电感引起的。基于这些考虑,电路中的潜在攻击者是:

a、高振幅信号 (电压或电流)

b、快速信号 (上升时间短或者高频)

最小化串扰的基本规则:使攻击者和受害者尽可能远离。

具体规则如下:

二带状线布置

串扰的明显对策是使攻击者和受害者尽可能远离,以避免耦合电容和电感。这样做的第一步是避免在同一层上有攻击者和受害者。

布线层之间的参考平面将大大减少这些层上信号之间的串扰,因此,如果可能,将攻击者和受害者分配给至少由接地层或供电层隔开的不同层。

带状线层上的串扰比微带线层上的串扰小,因此,如果攻击者和受害者必须共享同一区域和同一层,则它应该是带状线层。

三正交布线

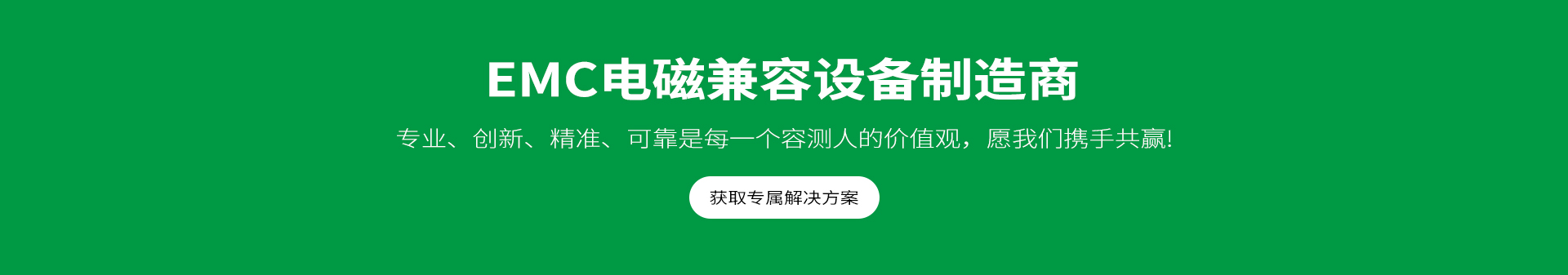

通过为每个层分配单个方向并交替相邻层的方向,可以大大减少电容耦合和电感耦合。该技术称为“正交布线”,如图1所示。

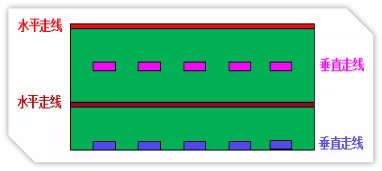

当不能应用正交布线或对于没有被参考平面分隔的具有相同布线方向的层时,也可以通过交错信号迹线来减少串扰,如图2所示。

四平行布线

如果无法在不同层上布置攻击者和受害者,则应强制按照并行走线要求进行布线。平行走线之间的串扰噪声量取决于平行走线的长度和它们之间的间隙。间隙越小,对于相同的串扰量,允许并行走线的长度越短。串扰不仅取决于并行度,而且还取决于信号和PCB特性。

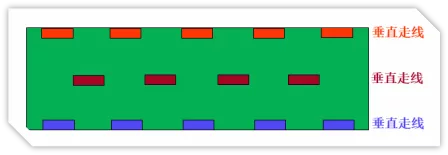

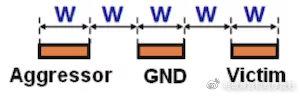

关于并行布线的经验法则称为“ 3W规则 ”,意思是为了避免在同一层布线的平行走线之间发生串扰,走线中心之间的最小间距应保持3W,图3说明了3W规则。

虽然通过应用3W规则确实可以减少串扰,但实际的3W值会导致电路板面积增大,可能很昂贵。因此通常在前边规则无法满足要求的情况下才使用3W规则。

五地防护线

减少在同一层上布线的平行走线之间串扰的另一种措施是使用两端都接地的走线(称为保护走线)将它们分开。图4中必须将保护走线的所有末端都接地,否则它将像天线一样把干扰带出去。

对防护技术的实验研究表明,通过简单地将受害者与攻击者分开,即使不存在防护走线,也可以实现相同的串扰降低(这等效于4W并行度规则)。但是,保护走线也会对周围环境的电磁干扰产生有益的影响,因此,仍然建议保留地线来减少强干扰信号和敏感信号的串扰。

保护走线会影响信号走线的特征阻抗和传输时间,如果将其应用于高速信号线需考虑信号完整性!

【声明】文章信息来源于互联网,目的在于传递更多信息,如转载内容涉及版权等问题,请立即与我们联系删除。

长沙容测电子有限公司致力于电磁兼容测试设备的研发以及电磁兼容测试技术的推广普及,全力为客户提供专业的EMC测试产品和解决方案。EMC电磁兼容测试仪主要有:军工EMC测试设备,48V汽车电子可编程电源,汽车电气性能测试设备,BCI大电流注入,新能汽车EMC测试设备,群脉冲测试仪,雷击浪涌发生器,阻尼振荡波测试仪,静电放电发生器,电压跌落发生器等。